### 32-Bit Mikrocontroller

Marktspezifische Spezialisierung bekannter Mikroprozessoren

- Steuerung/Regelung -> Mikrocontroller

- ► Flexible, vielfältige I/Os

- Harte Echtzeitbedingungen

- Sehr rauhe Umgebung

- Audio, Video, Signalverarbeitung -> DSP (Digitaler Signalprozessor)

- Hohe Rechenleistung

- Multiplikation/Addition/Schleife

- Universalrechner -> RISC (Reduced Instruction Set Computer)

- Großer Adressraum, Speicherplatzverwaltung

- Große Anzahl von Operationen/s

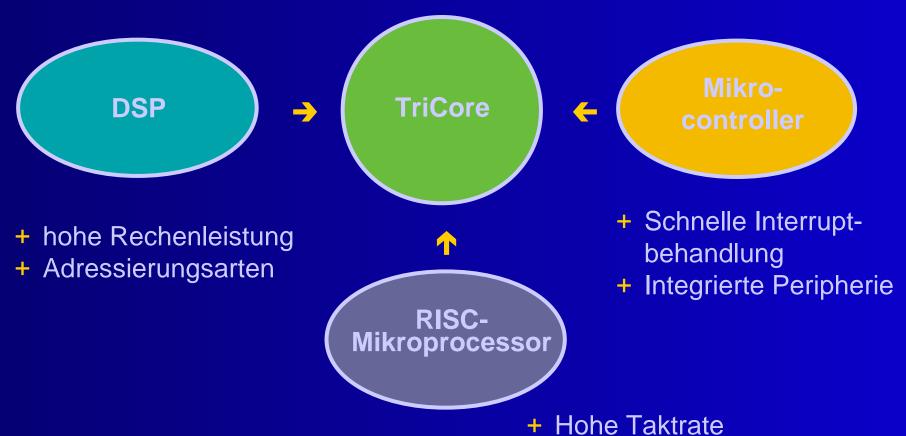

# TriCore Familie - High Performance 32-Bit Mikrocontroller

- Microcontroller-DSP Core

- Load/Store Architektur (RISC)

- Zwei 16x16 Bit MACs

- Schneller Kontextwechsel

- Superskalares Design mit 3 Pipelines

- 4 GB Adressbereich

- Flexible Schnittstellen

- Interruptsystem

- I/O Prozessor

- Speicher

- Memory Management Unit

- Je 24 KB Daten- und Programmspeicher

- Je 8 KB Daten- und Programm-Cache

- Emulation und Debug Unterstützung

### **TriCore Konzept**

- Entwickelt für Echtzeitsysteme im "Automotive"-Bereich

- Kombination der Stärken von 3 bewährten Architekturen

+ Große Anzahl Register

# TriCore: Mikrocontroller Eigenschaften

- Schneller Kontextwechsel (2 Taktzyklen)

- Schnelle Interruptbearbeitung

- Geringe Programmgröße durch Mix von 16-Bit und 32-Bit Befehlen

- Leistungsfähige Bit Manipulation

- Leistungsfähige Vergleichsbefehle

- Leistungsfähige integrierte Peripherie

# TriCore: DSP Eigenschaften

- Harvard Architektur zum parallelen Laden von Daten und Befehlen

- 16x16-Bit Multiplikation/Akkumulation in 1 Taktzyklus (Skalarproduktberechnung)

- Kompakte SIMD (Singular Instruction Multiple Data) Befehle z.B. für FFT

- DSP Adressierarten z.B. für diskrete Filter, Ringpuffer, ...

- Kein Schleifen-Overhead (autoincrement)

- Arithmetik

- Begrenzung

- Runden

- Allgemeine Mathematik

# TriCore: RISC Eigenschaften

- ▶ 32-Bit Load/Store Harvard Architektur

- Super-skalare Befehlsausführung

- ▶ 3 parallele 4-stufige Pipelines

- 2 universelle Registerbänke mit je 16 Registern für Daten und Adressen

- Speicherschutzmechanismen für Programm und Daten

- Hochsprachenunterstützung

- Betriebssystemunterstützung

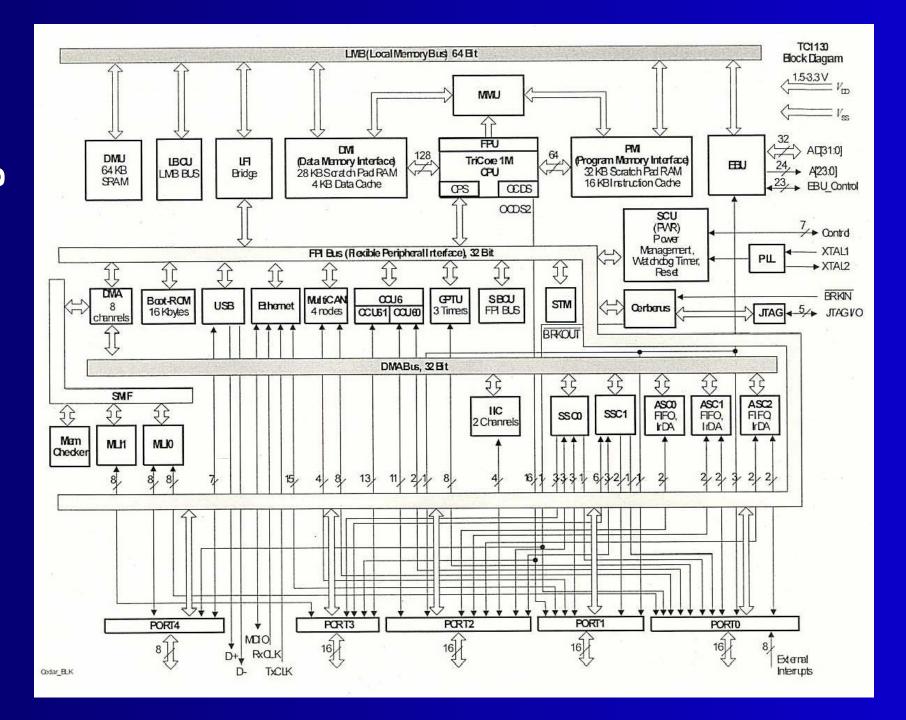

### **TriCore Architektur I**

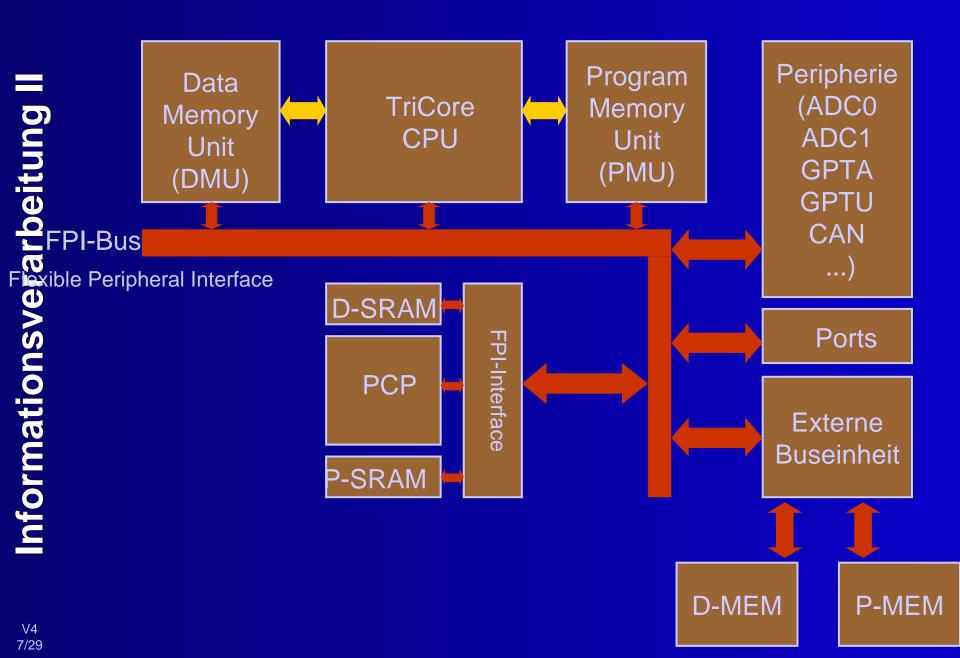

### TriCore Architektur II

- PMU Program Memory Unit (intern)

- ► 1 Zyklus Zugriffszeit

- bis 64K Gesamtspeicher, bis 16K Cache

- DMU Data Memory Unit (intern)

- ► 1 Zyklus Zugriffszeit

- bis 64K Gesamtspeicher, bis 16K Cache

- ► FPI Flexible Peripheral Interface: Anschluss von Peripherie

- PCP Peripheral Control Processor

- P\_MEM externer Programmspeicher

- D\_MEM externer Datenspeicher

- MMU Memory Management Unit (optional)

- FPU Floating Point Unit (optional)

# Informationsverarbeitung

### **TriCore Architektur III**

- Harvard Architektur mit separaten Adress- und Datenbussen. Laden von Befehlen und Daten erfolgt parallel.

- Superskalarer Kern mit 2 Hauptpipelines (je 4 Stufen) und 1 Zusatzpipeline für Schleifen. Alle 3 Pipelines arbeiten parallel.

- ► RISC Load/Store Maschine. Alle arithmetischen Befehle arbeiten mit Registern. 2 General-Purpose Registerbänke mit je 16 Registern für Daten und Adressen.

- Integer Execute Unit mit Multiply Accumulate Module (MAC) und Arithmetik and Logik Einheit (ALU).

- ► Hohe Integerrechenleistung: Zwei 16 x 16 Multiplikation/Addition pro Taktzyklus.

- ► Flexibler Peripheral Interconnect Bus (FPI Bus) verbindet Kern, Speicher, interne und externe Peripherie oder andere CPUs. .

- Minimalkonfiguration nur CPU und Core-Module. Peripherie- und Speichermodule können ergänzt werden.

# **Central Processing Unit (CPU)**

- ▶ 32-bit Festkomma-Arithmetik mit f<sub>CPU</sub> = 40MHz (Tricore 2 bis 600MHz)

- 4 Gbyte Adressbereich jeweils für Daten- und Codespeicher

- Spezielle Adressierungsarten (Circular buffer, bit-reverse) für DSP-Algorithmen

- Gemischter Befehlssatz aus 32- und 16-bit Befehlen

- Unterstützung von:

- Integer-Arithmetik (Kombinierte Befehle, Begrenzung)

- DSP-Arithmetik (Skalieren, Runden)

- Bitmanipulation (komplexe Boolsche Algebra)

- Schnelles Wechseln zwischen Tasks (z.B. Funktionsaufrufe, Interrupts) durch Hardware-Mechanismus

# Informationsverarbeitung

### **CPU-Pipelines**

3 Pipelines: parallele Ausführung von bis zu 3 Operationen

### Fetch

Decode Execute Write Back

Integer Unit

- Integer Arithmetik und logische Operationen

- ► Bitweise Operationen

- Multiplikation/Akkumulation (MAC)

- ► Integer Division

- ► Bedingte Sprünge

Decode Execute Write Back

Load/Store Unit

- Speichern/Laden

- ► Kontextwechsel

- Systemoperationen

- Adressrechnung für absolute und bedingte Sprünge

Cache Buffer Loop Loop

Loop Unit

- Zwischenspeicher

- Schleifenberechnung

- Überprüfung der Abbruchbedingung

z.B.: Zwei 16\*16-bit Multiplikations-/Additionsbefehle + Laden der nächsten Operanden + Schleifenbedingung in einem Clock-Zyklus

# Peripheral Control Processor (PCP)

- Datenübertragung zwischen beliebigen Speicheradressen ohne CPU Belastung

- → DMA-Controller (Direct Memory Access)

- Interrupt-Abarbeitung

- → Übernimmt Funktion von Teilen des Interrupt-Handlers

- Parallele Abarbeitung von bis zu 64 Ereignissen, generiert durch Peripherie ohne CPU-Interrupt - z.B.

- Timer-Reload

- Start/Stop eines Timers oder einer AD-Wandlung

- Berechnung des nächsten Compare-Wertes für PWM

- Durchführung logischer und arithmetischer Operationen

### Interruptsystem

- Interrupts generiert von Peripherie-Einheiten, CPU, PCP

- →105 Serviceknoten (SRN)

- Control-Register für SRN

- Aktivieren/Deaktivieren

- Prioritätsfestlegung

- Abarbeitung durch CPU oder PCP

- Status Bit (aktiv/nicht aktiv)

- Software-Aktivieren/Löschen

- Interruptbehandlung durch CPU oder PCP

- → 2 Kontrolleinheiten bedienen CPU oder PCP über entsprechende Busse

- Interruptvektortabelle geordnet nach Prioritäten

- → 256 verschiedene Level

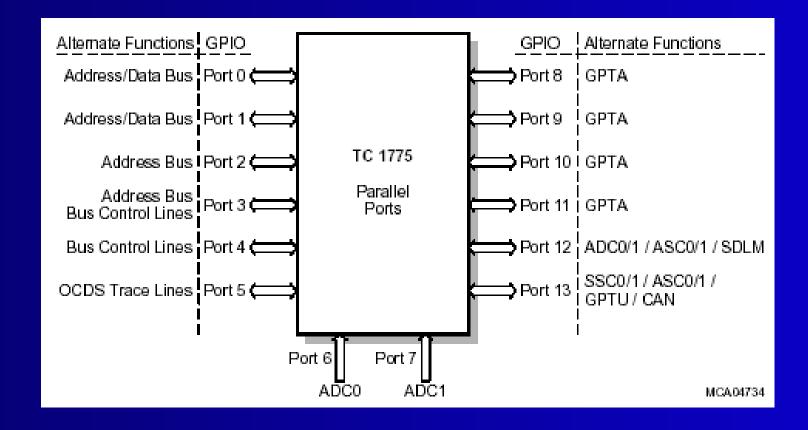

### **Parallel Ports**

- 192 digitale Ein-/ Ausgänge aufgeteilt in 12 16-Bit Ports: P0-P5 und P8-P13

- Zusätzlich 32 analoge Eingänge aufgeteilt in 2 16-Bit Ports: P6, P7

# Multitasking

- Hardwareunterstützung für schnellen Kontextwechsel

- Automatische Sicherung eines Teils der Prozessorregister bei erforderlichem Kontextwechsel und

- Automatische Wiederherstellung bei Rückkehr

- Automatische Verwaltung der Speicherbereiche für die geretteten Kontexte

- Zwei unabhängige Stackpointer

- Für Nutzung durch Compiler bzw. für Nutzung in Interrupt Service Routinen

- Stackpointer liegt im Register (A10) und wird für jede Task automatisch gerettet

### **On-Chip Peripherie**

- 2 Analog-Digital-Wandler Einheiten (ADC0, ADC1)

- General Purpose Timer Unit (GPTU)

- Drei 32-bit Timer/Counter

- General Purpose Timer Array (GPTA)

- Komplexe Verarbeitung und Generierung von I/O Signalen

- Serial Data Link Modul J1850 (KFZ-Schnittstelle)

- CAN Modul

- 2 Synchrone/Asynchchrone Serielle Schnittstellen (bis 1.25 MBaud)

- 2 High Speed Synchrone Serielle Schnittstellen (bis 380 MBaud)

- Watchdog Timer und System Timer

# Serial Data Link Module (SDLM)

- Kompatibel mit SAE J1850 (Kfz-Standard für Diagnose)

- Zweidrahtbus

- ► 10.4 bzw. 41.6 kBaud Übertragungsrate

- Digitaler Störfilter

- CRC (Cyclic Redundancy Check) Erzeugung und Überprüfung

- Interruptbetrieb

- Typisch für automotive Prozessor

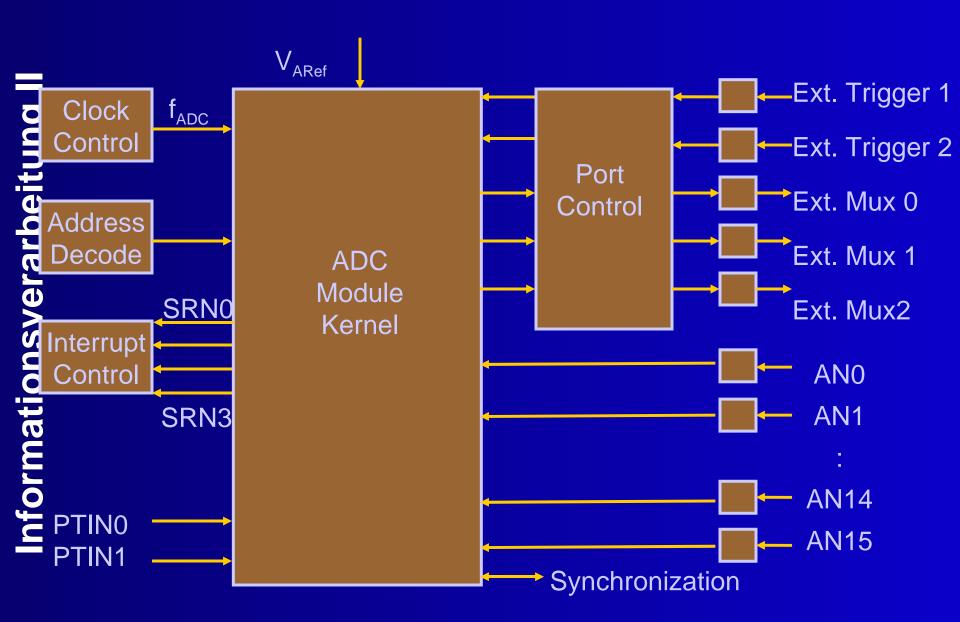

# **Analog-Digital-Wandler (ADC)**

- 2 gleichartige ADC Einheiten (ADC0, ADC1)

- ► 16 Kanäle über Multiplexer, integrierter S&H

- Wählbar 8-Bit, 10-Bit oder 12-Bit Auflösung

- Fehler ±2 LSB bei 10 Bit Auflösung

- Wandlungszeit 6µs @10-bit und 40MHz Clock

- Wählbare Referenzspannungen für jeden Kanal

- Detektion von Leitungsunterbrechung / Kurzschluss am Eingang

- Eingangsspannungsüberwachung (min, max)

- Modi

- Parallel: Gleichzeitige Anforderung mehrerer Kanäle, interne Arbitrierung

- Sequentiell: Einzelanforderung eines Kanals

- Triggerquellen:

- Timer, Externes Ereignis, Software, ...

### **Blockschaltbild ADC**

# **General Purpose Timer Unit (GPTU)**

- Drei 32 Bit Zähler

- 8 digitale Ein-/Ausgänge

- ►  $f_{max} = f_{CPU}$  → sehr feine Auflösung

- Kaskadierung zu 64 Bit Zähler

- Reload on Overflow

- Auf- bzw. Abwärtszähler

- Event- bzw. Interrupterzeugung

- sehr universelle Zählerfunktionen mit hoher Genauigkeit

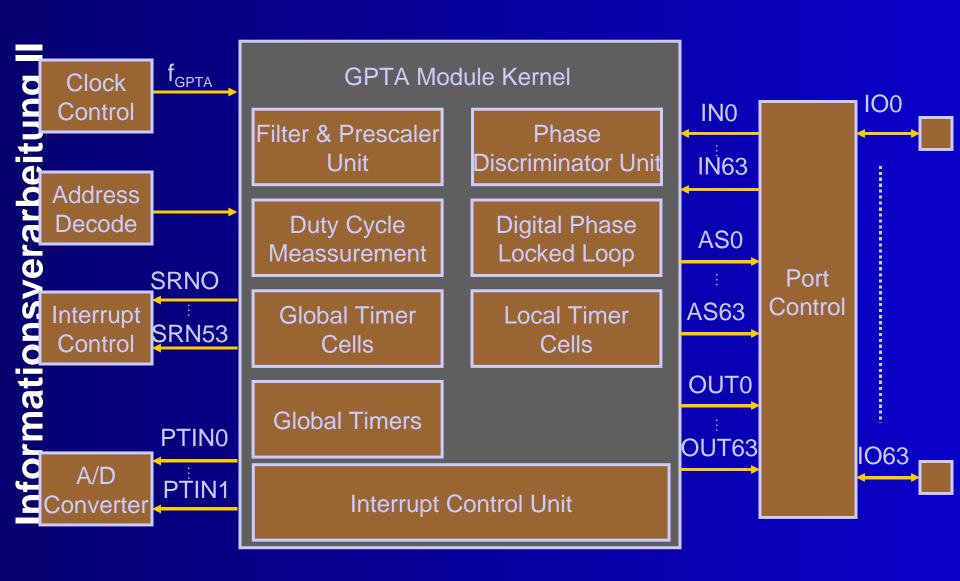

### **General Purpose Timer Array (GPTA)**

- Auswertung und Steuerung zeit- und ereignisgetriebener Aktivitäten der Ein- und Ausgänge

- CLock Generation Unit

- Filter, Frequenzteiler

- Phasendiskriminator (Phasenmessung für 2 und 3 Signale)

- Tastverhältnismessung

- Digitale PLL (Phase-Locked-Loop)

- Signal Generation Unit

- 2 globale Timer mit 24 Bit

- 32 globale Timer Zellen mit 24 Bit (Capture, Compare, ...)

- ► 64 lokale Timer Zellen mit 16 Bit (Timer, Capture, Compare)

- Interrupt Control Unit

- 111 Ereignisse für Interrupts über 54 Kanäle (SRN)

### **Blockschaltbild GPTA**

### Mitglieder der TriCore 1 Familie

► TC1775

32-Bit Mikrocontroller für anspruchsvolle automobile und industrielle Anwendungen, wie Motormanagement, Starter-Generator, Feldorientierte Regelung und Robotik

► TC1765

Vergleichbar TC1775, leicht abgerüstete und preiswertere Version

► TC11IB

Hochintegrierter industrieller Kommunikationscontroller

► TC1920

TriCore basierender 32-Bit Telematik Controller

► TC1912

TriCore basierender 32-Bit Audio und Gateway Controller

TC1910

Vergleichbar TC1912, leicht abgerüstete und preiswertere Version

→ Verschiedene Derivate mit TriCore Kern ableitbar

Anzohl dar Dariyota üharaahaybar (Varalaiah, 2051)

# Weiterentwicklung TriCore 2

- ▶ 0.13 µm Technologie

- ► f<sub>max</sub> bis 600 MHz

- ▶ 900 MIPS

- 1200 MMACs (Multiplikationen/Akumulationen)

- Größe des Prozessorkerns (ohne Peripherie und Speicher): 3mm²,

- ▶ Leistungsaufnahme: 0.5 mW/MHz → P<sub>600</sub>=300 mW

- Prozessorleistung entwickelt sich kontinuierlich weiter

### Zusammenfassung

- TriCore = hochintegrierter 32-bit Mikrocontroller/DSP für Anwendungen im "Embedded Systems" Bereich

- Hohe Prozessorleistung + komplexe Peripherie

- Effiziente Programmierung durch Befehlssatz mit DSP- und mikrocontrollertypischen Befehlen

- Hardware Konzept gewährleistet Flexibilität beim Einsatz in der Steuer- und Regelungstechnik

### Hersteller 32-Bit Mikrocontrollern

- Infineon

- Motorola (DSP, Controller, PC, ...)

- ► Texas Instruments (DSP, ...)

- Analog Devices (DSP, ...)

- ► Intel (PC, Controller, ...)

- Philips

- Atmel

- Epson

- Hitachi

- **..**

### **Zusammenfassung 32-Bit Prozessoren**

- ▶ Vorteile

- ► Vollständiger, optimierter Mikroprozessor

- Sehr hohe Rechenleistung

- Autonome Subsysteme On-Chip: Timing, Interrupt, I/O, ...

- Vorhanden (Weiterentwicklungspotential)

- Architektur insgesamt entspricht State-of-the-Art

- Kontinuierliche Weiterentwicklung ...

- ► Nachteile

- Relativ hoher Preis

- ► Große Bauform

- Hardware Overhead durch Vollständigkeit

- ► Weniger Derivate als bei 8-Bitern, geringere Anpassungsfähigkeit

- Fehlende Konfigurierbarkeit

# **Zusammenfassung Mikrocontroller**

| Wortbreite             | 8    | 16     | 32        |           |

|------------------------|------|--------|-----------|-----------|

| Typischer<br>Vertreter | 8051 | 80C167 | TriCore 1 | TriCore 2 |

| Takt<br>[MHz]          | 60   | 40     | 40        | 600       |

| MIPS                   | 60   | 60     | 60        | 900       |

| Preis €                | 1-5  | 15-25  | 40-60     | ?         |

| typisch                |      |        |           |           |

| Gehäuse                | DIP  | QFP    | BGA       |           |

| Pinzahl                | 44   | 144    | 260       |           |

# nformationsverarbeitung

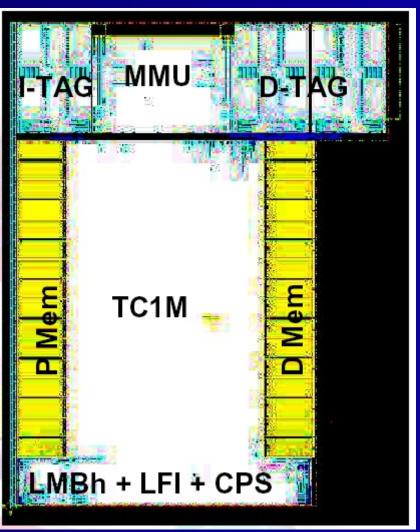

### **TriCore Hardmacro**

- TC1M = CPU + PMI + DMI

- 32kBytes Gesamtspeicher

- 16k Datenspeicher, mit 8k Cache

- 16k Programmspeicher, mit 8k Cache

- MMU

- ► LMBh, LFI, CPS

- Prozess: 0.18 µm

- Fläche: ~ 8.44 mm<sup>2</sup>

- Betriebsfrequenz: 200 MHz

- Betriebsspannung: 1.62V

- Zeitaufwand (spec freeze to tape/out): 4 Wochen

- Kosten: ?